It is important to find a SerDes core that has the right mixture of features needed for the targeted application. Besides cost and performance, there are many other factors to consider.

#High speed parallel to serial converter ic license

So, either from a cost point of view or a time-to-market point of view, instead of trying to develop the SerDes in-house, for most ASIC designers it makes more sense to license a proven SerDes IP core, unless a discrete SerDes is used which, in most cases, is not cost-effective anyway.īut not all SerDes cores are created equal.

It usually takes another year or so and maybe several design spins to make the SerDes mass-production possible. If the design is started from scratch, it is not unusual for a company to devote a mixed-signal design team for close to a year just to complete the design. Unfortunately, it is not an easy task to design a multi-gigabit SerDes due to the high-speed, mixed-signal circuitry involved and the stringent electrical specifications it has to meet. Simulated eye diagram after a 40-inch FR4 trace Attenuation caused by the lossy FR4 traces is much more severe at higher frequencyįigure 4. SerDes plays an essential role in serial data communicationsįigure 3. Therefore, reliable data transmission over a serial link relies heavily on the robust performance of the SerDes.įigure 2. In addition, reflections caused by impedance mismatch and crosstalks from nearby signals and other impediments can further degrade and corrupt the received signals. Figure 4 shows the eye diagram of a pseudo-random bit pattern after a 40-in FR4 trace. So, after traveling through some distance on a PCB or through a cable, the received data waveform can be severely distorted.

#High speed parallel to serial converter ic Pc

Furthermore, as shown in Figure 3, the amount of attenuation caused by the lossy FR4 traces on a PC board is significantly more severe at higher frequencies. But, the tradeoff for the increased data rate is now we have to recover the clock signal from the received serial data stream, which requires more complicated circuitry in the receiver.

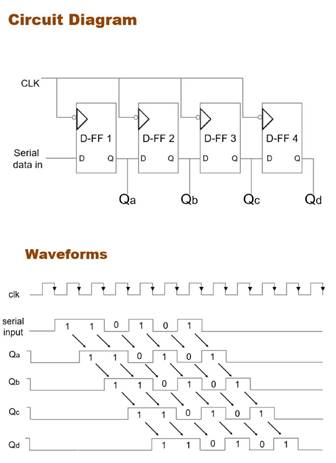

For instance, PCI Express specifies a serial data rate of 2.5Gb/s, which translates into a bit period of merely 400ps. As a result, a serial bus can usually operate at a much higher data rate than a parallel bus in a comparable system environment. Since there is no separate clock signal in a serial bus, timing skew between clock and data (which, together with the minimum setup and hold time, determines the maximum data transfer rate) no longer exists. The timing skew problem encountered in a parallel bus is solved by embedding the clock signal into the data stream. In essence, a SerDes is a serial transceiver which converts parallel data into a serial data stream on the transmitter side and converts the serial data back to parallel on the receiver side. The SerDes can be either a stand-alone device or, in most cases, an IP core integrated into a serial bus controller or an ASIC. In a serial bus, a device called SerDes (Serializer/ Desrializer) is used to transmit and receive data over the serial link as shown in Figure 2. Figure 1 shows a PCI Express based PC that would appear on the market in 2004.įigure 1. In the case of PCI and PCI-X, a serial replacement called PCI-Express (formerly known as 3GIO or Third Generation I/O) has been adopted by PCI-SIG and is supported by over 280 member companies in the Intel Developer Network for PCI Express Architecture. For example, the vintage IDE bus is being replaced by SATA (Serial ATA) and the parallel SCSI bus by SAS (Serial Attached SCSI). To circumvent the performance limitation and voltage scaling problem posed by the conventional parallel buses, there is an industry-wide mega-trend to migrate the multi-drop parallel buses to point-to-point serial buses. In addition, the relatively high voltage levels specified in the legacy parallel buses are incompatible with the reduced supply voltages used in advanced CMOS process technologies. For example, the tolerance in timing skew between parallel signals in a multi-drop environment is approaching the practical limit achievable in low-cost FR4 printed circuit boards. But it is getting more and more difficult to improve the performance with a multi-drop parallel bus such as PCI and PCI-X. Traditionally, the I/O- subsystems are connected to the CPU through the PCI or PCI-X bus. IntroductionĪs the CPU speed reaches 3GHz and beyond, the I/O performance of a PC has increasingly become the bottleneck of the overall system performance.

0 kommentar(er)

0 kommentar(er)